## Lecture Notes in Computer Science

4943

Commenced Publication in 1973

Founding and Former Series Editors:

Gerhard Goos, Juris Hartmanis, and Jan van Leeuwen

#### **Editorial Board**

David Hutchison

Lancaster University, UK

Takeo Kanade

Carnegie Mellon University, Pittsburgh, PA, USA

Josef Kittler

University of Surrey, Guildford, UK

Jon M. Kleinberg

Cornell University, Ithaca, NY, USA

Alfred Kobsa

University of California, Irvine, CA, USA

Friedemann Mattern

ETH Zurich, Switzerland

John C. Mitchell

Stanford University, CA, USA

Moni Naor

Weizmann Institute of Science, Rehovot, Israel

Oscar Nierstrasz

University of Bern, Switzerland

C. Pandu Rangan

Indian Institute of Technology, Madras, India

Bernhard Steffen

University of Dortmund, Germany

Madhu Sudan

Massachusetts Institute of Technology, MA, USA

Demetri Terzopoulos

University of California, Los Angeles, CA, USA

Doug Tygar

University of California, Berkeley, CA, USA

Gerhard Weikum

Max-Planck Institute of Computer Science, Saarbruecken, Germany

Roger Woods Katherine Compton Christos Bouganis Pedro C. Diniz (Eds.)

## Reconfigurable Computing: Architectures, Tools and Applications

4th International Workshop, ARC 2008 London, UK, March 26-28, 2008 Proceedings

#### Volume Editors

Roger Woods Queen's University Belfast ECIT Institute, Queen's Road, Queen's Island, Belfast, BT 3 9DT, UK E-mail: r.woods@qub.ac.uk

Katherine Compton University of Wisconsin-Madison 1415 Engineering Drive, Madison, WI 53706, USA E-mail: kati@engr.wisc.edu

Christos Bouganis Imperial College London Department of Electrical and Electronic Engineering South Kensington Campus, London, SW7 2AZ, UK E-mail: christos-savvas.bouganis@imperial.ac.uk

Pedro C. Diniz

Technical University of Lisbon

Instituto Superior Técnico, Av. Rovisco Pais, 1049-001 Lisboa, Portugal

E-mail: pedro.diniz@tagus.ist.utl.pt

Library of Congress Control Number: 2008923932

CR Subject Classification (1998): C, B, I.4

LNCS Sublibrary: SL 1 – Theoretical Computer Science and General Issues

ISSN 0302-9743

ISBN-10 3-540-78609-0 Springer Berlin Heidelberg New York ISBN-13 978-3-540-78609-2 Springer Berlin Heidelberg New York

This work is subject to copyright. All rights are reserved, whether the whole or part of the material is concerned, specifically the rights of translation, reprinting, re-use of illustrations, recitation, broadcasting, reproduction on microfilms or in any other way, and storage in data banks. Duplication of this publication or parts thereof is permitted only under the provisions of the German Copyright Law of September 9, 1965, in its current version, and permission for use must always be obtained from Springer. Violations are liable to prosecution under the German Copyright Law.

Springer is a part of Springer Science+Business Media

springer.com

© Springer-Verlag Berlin Heidelberg 2008 Printed in Germany

Typesetting: Camera-ready by author, data conversion by Scientific Publishing Services, Chennai, India Printed on acid-free paper SPIN: 12240425 06/3180 5 4 3 2 1 0

#### **Preface**

For many years, the idea of reconfigurable hardware systems has represented the *Holy Grail* for computer system designers. It has been recognized for a long time that the microprocessor provides high flexibility but at a very low performance merit in terms of MIPS/W or other such measures. *Reconfigurable systems* are thus attractive as they can be configured to provide the best match for the computational requirements at that specific time, giving much better area – speed – power performance.

However, the practicalities of achieving such a reconfigurable system are numerous and require the development of: suitable reconfigurable hardware to support the dynamic behavior; programming tools to allow the dynamic behavior of the reconfigurability to be modelled; programming languages to support reconfiguration; and verification techniques that can demonstrate that reconfiguration has happened correctly at each stage. While the problems are many, the existence and development of technologies such as the multi-core processor architecture, reconfigurable computing architectures, and application-specific processors suggest there is a strong desire for reconfigurable systems. Moreover, FPGAs also provide the ideal platforms for the development of such platforms.

The major motivation behind the International Workshop on Applied Reconfigurable Computing (ARC) series is to create a forum for presenting and discussing on-going research efforts in applied reconfigurable computing. The workshop also focuses on compiler and mapping techniques, and new reconfigurable computing architectures. The series of editions started in 2005 in Algarve, Portugal, followed by the 2006 workshop in Delft, The Netherlands, and last year's workshop in Mangaratiba, Rio de Janeiro, Brazil. As in previous years, selected papers have been published as a Springer LNCS (Lecture Notes in Computer Science) volume.

This LNCS volume includes the papers selected for the fourth edition of the Workshop (ARC 2008), held at Imperial College London, UK during March 26–28, 2008. The workshop attracted a large number of very good papers, describing interesting work on reconfigurable computing related subjects. A total of 56 papers were submitted to the workshop from 18 countries: UK (9), Republic of China (6), Germany (6), USA (5), The Netherlands (4), France (4), Greece (3), Portugal (3), Brazil (3), Republic of South Korea (2), Japan (2), Spain (2), Poland (2), India (1), Belgium (1), Turkey (1), Thailand (1) and Canada (1).

In most cases, submitted papers were evaluated by at least three members of the Program Committee. After careful selection, 21 papers were accepted as full papers (acceptance rate of 38.1%) and 14 as short papers (global acceptance rate of 63.6%). Those accepted papers led to a very interesting workshop program, which we consider to constitute a representative overview of on-going research efforts in reconfigurable computing, a rapidly evolving and maturing field.

#### VI Preface

Several people contributed to the success of the 2008 edition of the workshop. We would like to acknowledge the support of all the members of this year's workshop Steering and Program Committees in reviewing papers, in helping the paper selection, and in giving valuable suggestions. Special thanks also to the additional researchers who contributed to the reviewing process, to all the authors that submitted papers to the workshop, and to all the workshop attendees. Last but not least, we would like to thank Springer, and Alfred Hofmann in particular, for their continued support in publishing the proceedings as part of the LNCS series and to Jürgen Becker from the University of Karlsruhe for his continued support role.

January 2008

Roger Woods Katherine Compton Christos Bouganis Pedro C. Diniz

### **Organization**

#### Organizing Committee

General Chairs Christos-Savvas Bouganis (Imperial College

London, UK)

Pedro C. Diniz (Instituto Superior Técnico,

Portugal)

**Program Chairs** Katherine Compton (University of

Wisconsin-Madison, USA)

Roger Woods (Queen's University Belfast, UK) Pete Sedcole (Imperial College London, UK) Proceedings Chair Local Arrangements Chairs

Alastair Smith (Imperial College London, UK)

Terrence Mak (Imperial College London, UK) Iosifina Pournara (Birkbeck College, UK) Wiesia Hsissen (Imperial College London, UK)

### Steering Committee

Web Design

Secretary

George Constantinides Imperial College London, UK João M.P. Cardoso IST/INESC-ID, Portugal

Koen Bertels Delft University of Technology, The Netherlands Mladen Berekovic Braunschweig University of Technology, Germany

Pedro C. Diniz Instituto Superior Técnico, Portugal Walid Najjar University of California Riverside, USA

In memory of Stamatis Vassiliadis [1951–2007], Steering Committee Member for ARC 2006 and 2007.

#### Program Committee

Jeff Arnold Stretch Inc., USA

University of California, Irvine, USA Nader Bagherzadeh Jürgen Becker University of Karlsruhe (TH), Germany

Braunschweig University of Technology, Germany Mladen Berekovic

Neil Bergmann University of Queensland, Australia

Koen Bertels Delft University of Technology, The Netherlands

Christos-Savvas Bouganis Imperial College London, UK

Xilinx Corp., USA Gordon Brebner Mihai Budiu Microsoft Research, USA

Tim Callahan Carnegie Mellon University, USA

#### VIII Organization

João M.P. Cardoso IST/INESC-ID, Portugal

Mark Chang Olin College, USA

Peter Cheung Imperial College London, UK Paul Chow University of Toronto, Canada

Katherine Compton University of Wisconsin-Madison, USA

George Constantinides Imperial College London, UK

Oliver Diessel University of New South Wales, Australia Pedro C. Diniz Instituto Superior Técnico, Portugal Tarek El-Ghazawi George Washington University, USA

Robert Esser Xilinx Corp., Ireland

Antonio Ferrari University of Aveiro, Portugal

Reiner Hartenstein

Román Hermida

Ryan Kastner

Andreas Koch

Philip Leong

University of Kaiserslautern, Germany

Complutense University of Madrid, Spain

University of California, Santa Barbara, USA

Darmstadt University of Technology, Germany

Chinese University of Hong Kong, China

Wayne Luk Imperial College London, UK John McAllister Queen's University Belfast, UK

Maria-Cristina Marinescu IBM T.J. Watson Research Center, USA

Eduardo Marques University of São Paulo, Brazil Kostas Masselos University of Peloponnese, Greece Seda Ö. Memik Northwestern University, USA Oskar Mencer Imperial College London, UK

Walid Najjar University of California Riverside, USA

Horácio Neto INESC-ID/IST, Portugal

Joon-seok Park Inha University, Seoul, South Korea

Andy Pimentel University of Amsterdam, The Netherlands

Joachim Pistorius Altera Corp., USA

Marco Platzner University of Paderborn, Germany Bernard Pottier University of Bretagne, France

Tsutomu Sasao Kyushu Institute of Technology, Japan

Pete Sedcole Imperial College London, UK

Lesley Shannon Simon Fraser University, USA

Russell Tessier University of Massachusetts, USA

Pedro Trancoso University of Cyprus, Cyprus

Ranga Vemuri University of Cincinnati, USA

Markus Weinhardt PACT Informationstechnologie AG, Germany Stephan Wong Delft University of Technology, The Netherlands

Roger Woods Queen's University Belfast, UK

#### Additional Reviewers

Esther Andres Qiang Liu

Kubilay Atasu Antonio Roldao Lopes

Alberto del Barrio Enno Lübbers

David Boland Yi Lu

Vanderlei Bonato Lars Braun Hagen Gädke Carlo Galuzzi

Angamuthu Ganesan

Heiner Giefers Jose I. Gomez Laiq Hasan

José Arnaldo Mascagni de Holanda

Jae Young Hur Matthias Kuehnle Mahendra Kumar Loic Lagadec Y.M. Lam

Martin Langhammer

Terrence Mak

Thomas Marconi

Shahnam Mirzaei

Abhishek Mitra

Shinobu Nagayama

Juanjo Noguera

Christian Plessl

Fredy Rivera

Mojtaba Sabeghi

Thomas Schuster

K. Susanto

Timothy Todman Kieron Turkington

Qiang Wu

## **Table of Contents**

| Keynotes                                                                                |    |

|-----------------------------------------------------------------------------------------|----|

| Synthesizing FPGA Circuits from Parallel Programs  Satnam Singh and David Greaves       | 1  |

| From Silicon to Science: The Long Road to Production Reconfigurable Supercomputing      | 2  |

| The von Neumann Syndrome and the CS Education Dilemma $Reiner\ Hartenstein$             | 3  |

| Programming and Compilation                                                             |    |

| Optimal Unroll Factor for Reconfigurable Architectures                                  | 4  |

| Programming Reconfigurable Decoupled Application Control Accelerator for Mobile Systems | 15 |

| DNA and String Processing Applications                                                  |    |

| DNA Physical Mapping on a Reconfigurable Platform                                       | 27 |

| Hardware BLAST Algorithms with Multi-seeds Detection and Parallel Extension             | 39 |

| Highly Space Efficient Counters for Perl Compatible Regular Expressions in FPGAs        | 51 |

| Scientific Applications                                                                 |    |

| A Custom Processor for a TDMA Solver in a CFD Application                               | 63 |

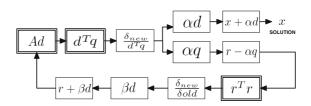

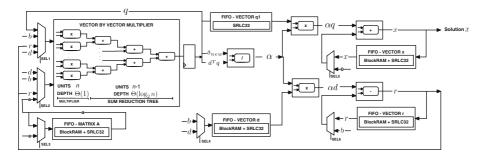

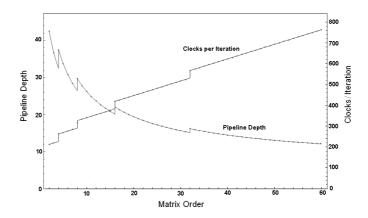

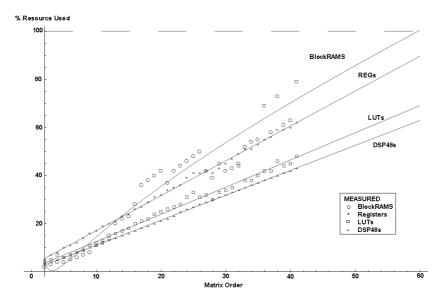

| A High Throughput FPGA-Based Floating Point Conjugate Gradient Implementation           | 75 |

| Reconfigurable Computing Hardware and Systems                                                                                   |     |

|---------------------------------------------------------------------------------------------------------------------------------|-----|

| Physical Design of FPGA Interconnect to Prevent Information                                                                     | 0.5 |

| Leakage                                                                                                                         | 87  |

| Symmetric Multiprocessor Design for Hybrid CPU/FPGA SoCs Shane Santner, Wesley Peck, Jason Agron, and David Andrews             | 99  |

| Run-Time Adaptable Architectures for Heterogeneous Behavior                                                                     |     |

| Embedded Systems                                                                                                                | 111 |

| Image Processing                                                                                                                |     |

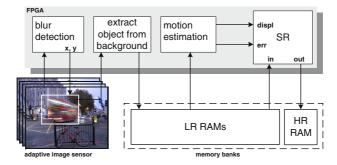

| FPGA-Based Real-Time Super-Resolution on an Adaptive Image Sensor                                                               | 125 |

| A Parallel Hardware Architecture for Image Feature Detection                                                                    | 137 |

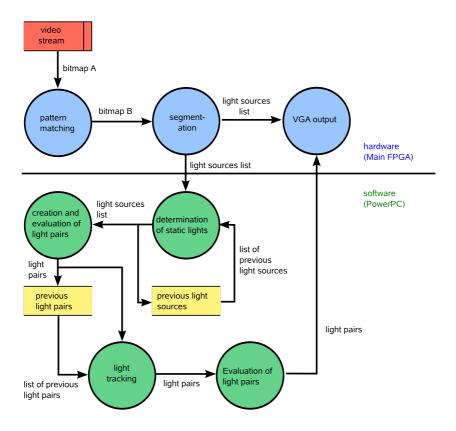

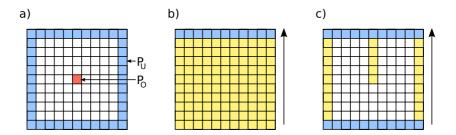

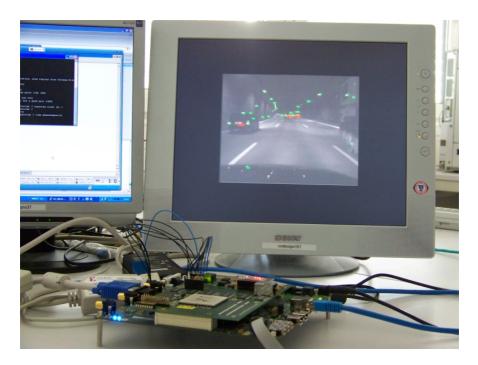

| Reconfigurable HW/SW Architecture of a Real-Time Driver Assistance                                                              |     |

| System                                                                                                                          | 149 |

| Run-Time Behavior                                                                                                               |     |

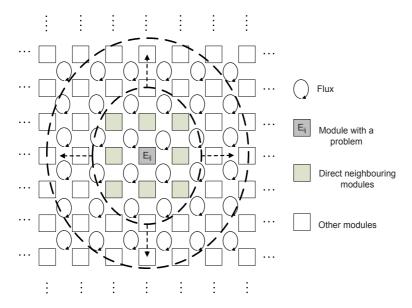

| A New Self-managing Hardware Design Approach for FPGA-Based Reconfigurable Systems                                              | 160 |

| A Preemption Algorithm for a Multitasking Environment on<br>Dynamically Reconfigurable Processor                                | 172 |

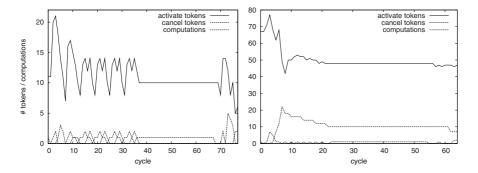

| Accelerating Speculative Execution in High-Level Synthesis with Cancel Tokens                                                   | 185 |

| Instruction Set Extension                                                                                                       |     |

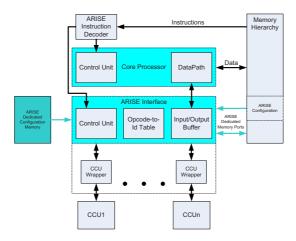

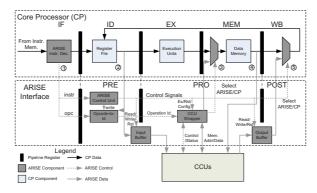

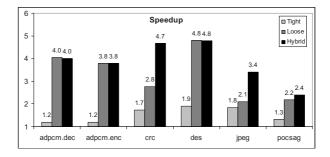

| ARISE Machines: Extending Processors with Hybrid Accelerators Nikolaos Vassiliadis. George Theodoridis. and Spiridon Nikolaidis | 196 |

| Table of Contents                                                                                                                                                         | XIII |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| The Instruction-Set Extension Problem: A Survey                                                                                                                           | 209  |

| Random Number Generation and Financial<br>Computation                                                                                                                     |      |

| An FPGA Run-Time Parameterisable Log-Normal Random Number Generator                                                                                                       | 221  |

| Multivariate Gaussian Random Number Generator Targeting Specific Resource Utilization in an FPGA                                                                          | 233  |

| Exploring Reconfigurable Architectures for Binomial-Tree Pricing Models                                                                                                   | 245  |

| Posters                                                                                                                                                                   |      |

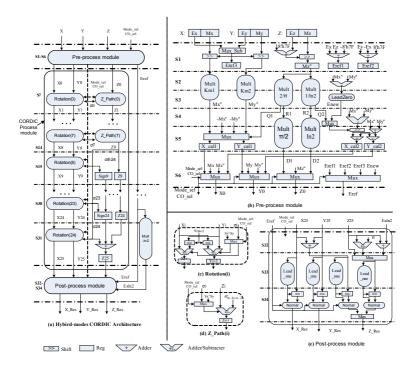

| Hybrid-Mode Floating-Point FPGA CORDIC Co-processor  Jie Zhou, Yong Dou, Yuanwu Lei, and Yazhuo Dong                                                                      | 256  |

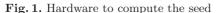

| Multiplier-Based Double Precision Floating Point Divider According to the IEEE-754 Standard                                                                               | 262  |

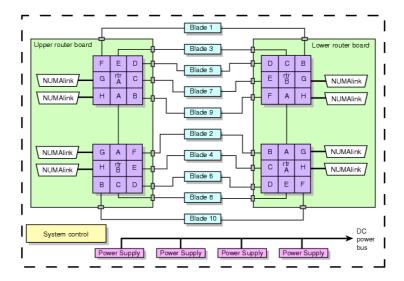

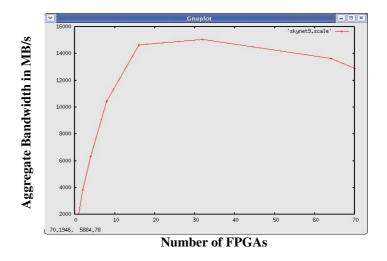

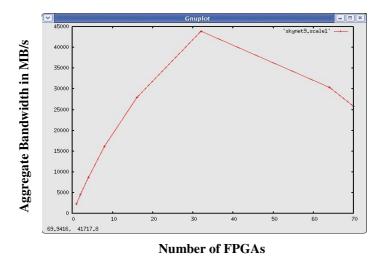

| Creating the World's Largest Reconfigurable Supercomputing System Based on the Scalable SGI® Altix® 4700 System Infrastructure and Benchmarking Life-Science Applications | 268  |

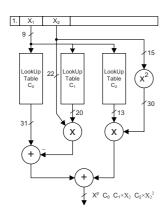

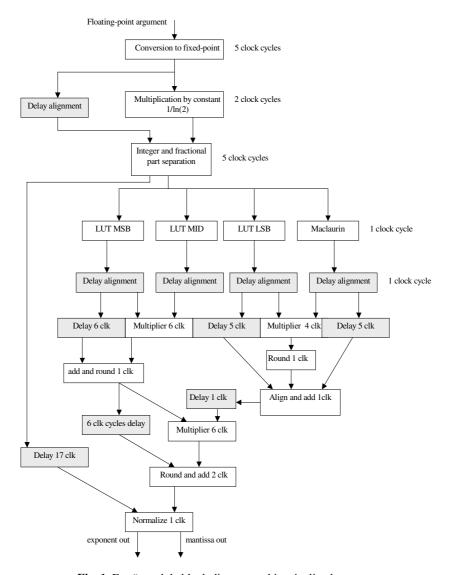

| Highly Efficient Structure of 64-Bit Exponential Function Implemented in FPGAs                                                                                            | 274  |

| A Framework for the Automatic Generation of Instruction-Set Extensions for Reconfigurable Architectures                                                                   | 280  |

| PARO: Synthesis of Hardware Accelerators for Multi-dimensional Dataflow-Intensive Applications                                                                            | 287  |

#### XIV Table of Contents

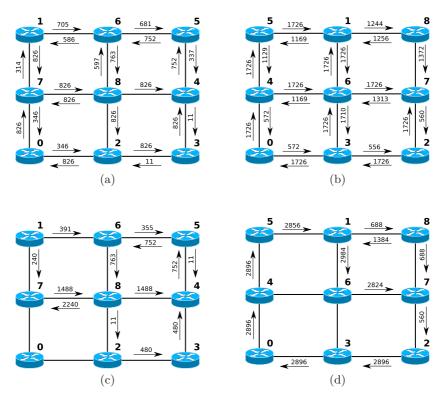

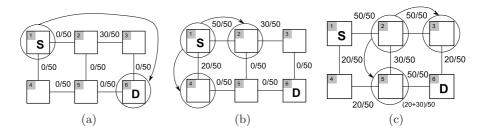

| Stream Transfer Balancing Scheme Utilizing Multi-path Routing in Networks on Chip                                          | 294 |

|----------------------------------------------------------------------------------------------------------------------------|-----|

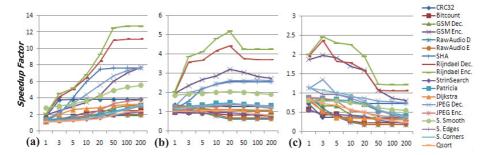

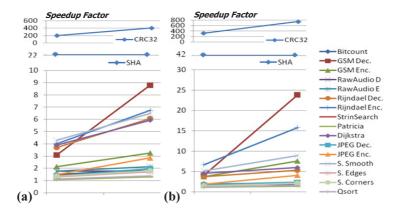

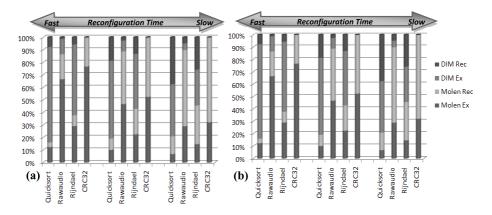

| Efficiency of Dynamic Reconfigurable Datapath Extensions – A Case Study                                                    | 300 |

| Online Hardware Task Scheduling and Placement Algorithm on<br>Partially Reconfigurable Devices                             | 306 |

| Data Reallocation by Exploiting FPGA Configuration Mechanisms Oliver Sander, Lars Braun, Michael Hübner, and Jürgen Becker | 312 |

| A Networked, Lightweight and Partially Reconfigurable Platform                                                             | 318 |

| Neuromolecularware – A Bio-inspired Evolvable Hardware and Its<br>Application to Medical Diagnosis                         | 324 |

| An FPGA Configuration Scheme for Bitstream Protection                                                                      | 330 |

| Lossless Compression for Space Imagery in a Dynamically Reconfigurable Architecture                                        | 336 |

| Author Index                                                                                                               | 343 |

# Synthesizing FPGA Circuits from Parallel Programs

Satnam Singh<sup>1</sup> and David Greaves<sup>2</sup>

Microsoft Research Cambridge, UK Cambridge University, UK

Abstract. In this presentation we describe recent experiments to represent circuit descriptions as explicit parallel programs written in regular programming languages rather than hardware description languages. Although there has been much work on compiling sequential C-like programs to hardware by automatically "discovering" parallelism we work by exploiting the parallel architecture communicated by the designer through the choice of parallel and concurrent programming language constructs. Specially, we describe a system that takes .NET assembly language with suitable custom attributes as input and produces Verilog output which is mapped to FPGAs. We can then choose to apply analysis and verification techniques to either the high level representation in C# or other .NET languages or to the generated RTL netlisits.

## From Silicon to Science: The Long Road to Production Reconfigurable Supercomputing

Keith Underwood

Intel Corporation, USA

Abstract. Over the last several years, multiple vendors have introduced systems that integrate FPGAs, as well as other types of accelerators, into machines intended for general purpose supercomputing. However, these machines have not broadly penetrated production scientific computing at any of the world's top supercomputing centers. With the excitement around accelerators and the numerous examples of their potential, why haven't they achieved widespread adoption in production supercomputing? This talk will discuss several barriers to adoption based on input from people who buy supercomputers and from people who use them. The short answer is that FPGA enhanced supercomputers look very little like traditional supercomputers and the performance advantage for scientific applications is often not as compelling as advertised. This talk will attempt to map barriers to adoption to specific research challenges that must be addressed to see widespread usage of FPGAs for scientific computing. These challenges include everything from the lowest level of circuit design to the programming of applications, and point to a lot of work between the current state of the art and widespread adoption of reconfigurable computing.

## The von Neumann Syndrome and the CS Education Dilemma

Reiner Hartenstein

Technical University of Kaiserslautern, Germany http://hartenstein.de/

Abstract. Computing the von Neumann style is tremendously inefficient because multiple layers of massive overhead phenomena often lead to code sizes of astronomic dimensions, thus requiring large capacity slow off-chip memory. The dominance of von-Neumann-based computing will become unaffordable during next decade because of growing very high energy consumption and increasing cost of energy. For most application domains a von-Neumann-based parallelization does not scale well, resulting in the escalating many-core programming crisis by requiring complete remapping and re-implementation—often promising only disappointing results. A sufficiently large population of manycore-qualified programmers is far from being available. Efficient solutions for the many-core crisis are hardly possible by fully instruction-stream-based approaches. Several HPC celebrities call for a radical re-design of the entire computing discipline. The solution is a dual paradigm approach, which includes fundamental concepts known already for a long time from Reconfigurable Computing. Whistle blowing is overdue, since these essential qualifications for our many-core future and for low energy computing are obstinately ignored by CE, CS and IT curriculum task forces. This talk also sketches a road map.

# Optimal Unroll Factor for Reconfigurable Architectures

Ozana Silvia Dragomir, Elena Moscu-Panainte, Koen Bertels, and Stephan Wong

Computer Engineering, EEMCS, Delft University of Technology,

Mekelweg 4, 2628 CD Delft, The Netherlands

{0.S.Dragomir,E.Moscu-Panainte,K.L.M.Bertels,J.S.S.M.Wong}@tudelft.nl

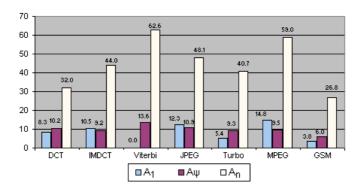

Abstract. Loops are an important source of optimization. In this paper, we address such optimizations for those cases when loops contain kernels mapped on reconfigurable fabric. We assume the Molen machine organization and Molen programming paradigm as our framework. The proposed algorithm computes the optimal unroll factor u for a loop that contains a hardware kernel K such that u instances of K run in parallel on the reconfigurable hardware, and the targeted balance between performance and resource usage is achieved. The parameters of the algorithm consist of profiling information about the execution times for running K in both hardware and software, the memory transfers and the utilized area. In the experimental part, we illustrate this method by applying it to a loop nest from a real-life application (MPEG2), containing the DCT kernel.

#### 1 Introduction

Reconfigurable Computing (RC) is becoming increasingly popular and the common solution for obtaining a significant performance increase is to identify the application kernels and accelerate them on hardware. As loops represent an important source of performance improvement, we investigate how existing loop optimizations can be applied when hardware kernels exist in the loop body. Assuming the Molen machine organization [1] as our framework, we focus our research in the direction of parallelizing applications by executing multiple instances of the kernel in parallel on the reconfigurable hardware.

Optimal is defined in this paper as the largest feasible unroll factor, given area constraints, performance requirements and memory access constraints, taking into account also that multiple kernels may be mapped on the area. The contributions of this paper are: a) an algorithm to automatically determine the optimal unroll factor, based on profile information about memory transfers, available area, and software/hardware execution times; b) experimental results for a well known-kernel – DCT (Discrete Cosine Transformation), showing that the optimal unroll factor is 6, with a speedup of 9.55x and utilized area of 72%.

The paper is organized as follows. Section 2 introduces the background and related work. In Section 3, we give a general definition of the problem and present

R. Woods et al. (Eds.): ARC 2008, LNCS 4943, pp. 4–14, 2008.

the target architecture and application. We propose a method for solving the problem in Section 4 and show the results for a specific application in Section 5. Finally, concluding remarks and future work are presented in Section 6.

#### 2 Background and Related Work

The work presented in this paper is related to the Delft WorkBench (DWB) project. The DWB is a semi-automatic toolchain platform for integrated hardware-software co-design in the context of Custom Computing Machines (CCM) which targets the Molen polymorphic machine organization [1]. More specifically, the DWB supports the entire design process, as follows. The kernels are identified in the first stage of profiling and cost estimation. Next, the Molen compiler [2] generates the executable file, replacing function calls to the kernels implemented in hardware with specific instructions for hardware reconfiguration and execution, according to the Molen programming paradigm. An automatic tool for hardware generation (DWARV [3]) is used to transform the selected kernels into VHDL code targeting the Molen platform.

Several approaches – [4], [5], [6], [7], [8], [9] are focused on accelerating kernel loops in hardware. Our approach is different, as we do not aggressively optimize the kernel implementation, but we focus on the optimization of the application for any hardware implementation, by executing multiple kernel instances in parallel.

PARLGRAN [10] is an approach that tries to maximize performance on reconfigurable architectures by selecting the parallelism granularity for each individual data-parallel task. However, this approach is different than ours in several ways: (i) they target task chains and make a decision on the parallelism granularity of each task, while we target loops (loop nests) with kernels inside them and make a decision on the unroll factor; (ii) in their case, the task instances have identical area requirements but different workloads, which translates into different executions time (a task is split into several sub-tasks); in our algorithm, all instances have the same characteristics in both area consumption and execution time; (iii) their algorithm takes into consideration the physical (placement) constraints and reconfiguration overhead at run-time, but without taking into account the memory bottleneck problem; we present a compile-time algorithm, which considers that there is no latency due to configuration of the kernels (static configurations), but takes into account the memory transfers.

#### 3 Problem Statement

Loops represent an important source of optimization, and there are a number of loop transformations (such as loop unrolling, software pipelining, loop shifting, loop distribution, loop merging, loop tiling, etc) that are used to maximize the parallelism inside the loop and improve the performance. The applications

we target in our work have loops that contain kernels inside them. One challenge we address is to improve the performance for such loops, by applying standard loop transformations such as the ones mentioned above.

In this paper, we focus on loop unrolling and present the assumptions and parameters for our model. Loop unrolling is a transformation that replicates the loop body and reduces the iteration number. Traditionally it is used to eliminate the loop overhead, thus improving the cache hit rate and reducing branching, while in reconfigurable computing it is used to expose parallelism.

The problem definition is: find the optimal unroll factor u of the loop (loop nest) with a kernel K, such that u identical instances of K run in parallel on the reconfigurable hardware, leading to the best balance between the performance and area utilization. The method proposed in this paper addresses this problem, given a C implementation of the target application and a VHDL implementation of the kernel.

We target the Molen framework, which allows multiple applications to run simultaneously on the reconfigurable hardware. The algorithm computes (at compile time) the optimal unroll factor, taking into consideration the memory transfers, the execution times in software and hardware, the area requirements for the kernel, and the available area (without physical details, P&R, etc). Thus, because of the reconfigurable hardware's flexibility, the algorithm's output depends on the hardware configuration at a certain time.

The main benefits of this algorithm are that it can be integrated in an automatic toolchain and it can use any hardware implementation of the kernel. Thus, performance can be improved even when the kernel is already optimized. Our assumptions regarding the application and the framework are presented below.

Target architecture. The Molen machine organization has been implemented on Vitex-II Pro XC2VP30 device, utilizing less than 2% of the available resources of the FPGA. The memory design uses the available on-chip memory blocks of the FPGA.

The factors taken into consideration by the proposed method are:

- area utilized by one kernel running on FPGA;

- available area (other kernels may be configured in the same time);

- execution time of the kernel in software and in hardware (in GPP cycles);

- the number of cycles for memory transfer operations for one kernel instance running in hardware;

- available memory bandwidth.

General and Molen-specific assumptions for the model:

- 1. There are no data dependencies between different iterations of the analyzed loop. Practical applications that satisfy this assumption exist, for example MPEG2 multimedia benchmark.

- 2. The loop bounds are known at compile time.

- 3. Inside the kernel, all memory reads are performed in the beginning and memory writes in the end. This does not reduce the generality of the problem for most applications.

- 4. The placement of the specific reconfiguration instructions is decided by a scheduling algorithm which runs after our algorithm, such that the configuration latency is hidden.

- 5. Only on-chip memory is used for program data. This memory is shared by the GPP and the CCUs.

- 6. All data that are necessary for all kernel instances are available in the shared memory.

- 7. The PowerPC and the CCU run at the same clock.

- 8. All transfers to/from the shared memory are performed sequentially.

- 9. Kernel's local variables/arrays are stored in the FPGA's local memory, such that all computations not involving the shared memory transfers can be parallelized.

- 10. As far as running multiple applications on the reconfigurable hardware is concerned, for now we take into consideration only the area constraints.

- 11. The area constraints do not include the shape of the design.

- 12. Additional area needed for interconnecting Molen with the kernels grows linearly with the number of kernels.

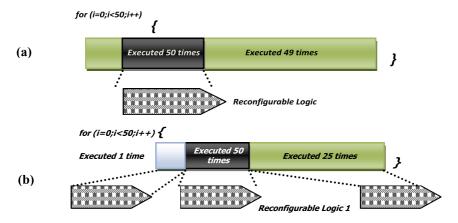

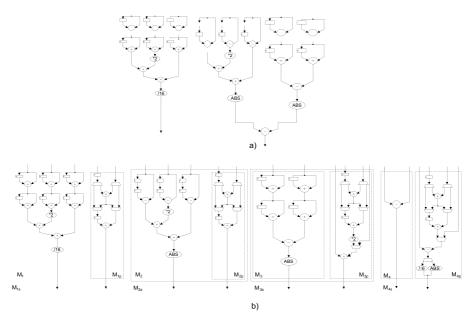

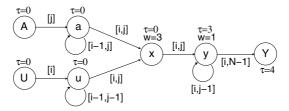

Motivational example. Throughout the paper, we will use the motivational example in Fig. 1(a). It consists of a loop with two functions – one function is executed always in software (CPar), and the other is the application kernel (K) – implicitly, the execution time for CPar is much smaller than for K. In each iteration i, data dependencies between CPar and K exist, as CPar computes the parameters for the kernel instance to be executed in the same iteration. The example has been extracted from the MPEG2 encoder multimedia benchmark, where the kernel K is DCT.

```

\begin{aligned} & \textbf{for} \; (i=0; \; i < N; \; i++ \;) \; \{ \\ & /^* \text{Compute parameters for} \\ & \text{K}()^* / \\ & \text{CPar} \; (i, \; blocks); \\ & /^* \text{Kernel function}^* / \\ & \text{K} \; (blocks[i]); \\ \} \end{aligned}

```

```

for (i = 0; i < N; i += u) {

CPar (i + 0, blocks);

...

CPar (i + u - 1, blocks);

/*u instances of K() in parallel*/

#pragma parallel

K (blocks[i + 0]);

...

K (blocks[i + u - 1]);

#end parallel

}

```

(a)Loop containing a kernel call

(b)Loop unrolled with a factor u

Fig. 1. Motivational example

#### 4 Proposed Methodology

In this section we present a method to determine the optimal unroll factor having as input the profiling information (execution time and number of memory transfers) area usage for one instance of the kernel. We illustrate the method by unrolling with factor u the code from Fig. 1(a). Figure 1(b) presents a simplified case when  $N \mod u = 0$ . Each iteration consists of u sequential executions of the function CPar() followed by the parallel execution of u kernel instances (there is an implicit synchronization point at the end of the parallel region).

**Area.** Taking into account only the area constraints and not the shape of the design, an upper bound for the unroll factor is set by

$$\mathbf{u_{a}} = \left\lfloor \frac{Area_{(available)}}{Area_{(K)} + Area_{(interconnect)}} \right\rfloor, \text{where:}$$

- $Area_{(available)}$  is the available area, taking into account the resources utilized by Molen and by other configurations;

- Area<sub>(interconnect)</sub> is the area necessary to connect one kernel with the rest of the hardware design (we made the assumption that the overall interconnect area grows linearly with the number of kernels);

- $Area_{(K)}$  is the area utilized by one instance of the kernel, including the storage space for the values read from the shared memory. All kernel instances have identical area requirements.

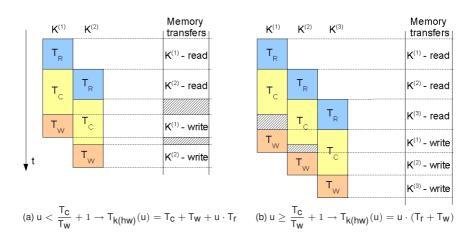

Memory accesses. In the ideal case, all data are available immediately and the degree of parallelism is bounded only by the area availability. However, for many applications, the memory bandwidth is an important bottleneck in achieving the ideal parallelism. We consider that  $T_{\rm r}$ ,  $T_{\rm w}$ , respectively  $T_{\rm c}$  are the times for memory read, write, and computation on hardware for kernel K. Then, the total time for running K in hardware is  $T_{\rm r} + T_{\rm w} + T_{\rm c}$ . Without reducing the generality of the problem for most applications, we assume that the memory reads are performed at the beginning and memory writes in the end. Then, as illustrated in Fig. 2, where we consider  $T_{\rm w} \leq T_{\rm r} < T_{\rm c}$  and  $T_{\rm r} + T_{\rm w} > T_{\rm c}$ , a new instance of K can start only after a time  $T_{\rm r}$  (we denote kernel instances by  $K^{(1)}$ ,  $K^{(2)}$ , etc)<sup>1</sup>.

The condition that memory access requests from different kernel instances do not overlap sets another bound  $(u_m)$  for the degree of unrolling on the reconfigurable hardware<sup>1</sup>:

$$u \cdot \min(T_{\mathrm{r}}, T_{\mathrm{W}}) \le \min(T_{\mathrm{r}}, T_{\mathrm{W}}) + T_{\mathrm{c}} \quad \Rightarrow \quad u \le u_{\mathrm{m}} = \left| \frac{T_{\mathrm{c}}}{\min(T_{\mathrm{r}}, T_{\mathrm{W}})} \right| + 1 \quad (1)$$

The time for running u instances of K on the reconfigurable hardware is<sup>1</sup>:

$$T_{K(\text{hw})}(u) = \begin{cases} T_{\text{C}} + T_{\text{F}} + T_{\text{W}} + (u - 1) \cdot \max(T_{\text{F}}, T_{\text{W}}) & \text{if } u < u_{\text{m}} \\ u \cdot (T_{\text{F}} + T_{\text{W}}) & \text{if } u \ge u_{\text{m}} \end{cases}$$

(2)

Since we are interested only in the case  $u < u_m$ , from (2) we derive the time for u instances of K in hardware as:

$$T_{K(hw)}(u) = T_{C} + \min(T_{r}, T_{w}) + u \cdot \max(T_{r}, T_{w})$$

(3)

Fig. 2. Parallelism on reconfigurable hardware

Note that when applied to the example in Fig. 2, the case  $u < u_{\rm m}$  corresponds to Fig. 2(a) and the case  $u \ge u_{\rm m}$  corresponds to Fig. 2(b). In our example,  $T_{\rm W} \le T_{\rm r}$ , thus  $\max(T_{\rm r}, T_{\rm W}) = T_{\rm r}$  and  $\min(T_{\rm r}, T_{\rm W}) = T_{\rm W}$ . In Fig. 2(a), the time for running in parallel two kernel instances  $(K^{(1)} \text{ and } K^{(2)})$  is given by the time for  $K^{(1)}$   $(T_{\rm c} + T_{\rm r} + T_{\rm w})$  plus the necessary delay for  $K^{(2)}$  to start  $(T_{\rm r})$ . In Fig. 2(b),  $K^{(1)}$  writing to memory is delayed because of  $K^{(3)}$  reading from memory; in this case, the actual kernel computation is hidden by the memory transfers and the hardware execution time depends only on the memory access times  $(u \cdot (T_{\rm r} + T_{\rm w}))$ .

**Speedup.** In order to compute the optimal unroll factor, we use the following notations:

- *N* initial number of iterations (before unrolling);

- N(u) number of iterations after unrolling with factor  $u: N(u) = \lceil N/u \rceil$ ;

- $T_{\text{SW}}$  number of cycles for that part of the loop body that is always executed by the GPP (in our example, the CPar function);

- $T_{K(sw)}$  /  $T_{K(hw)}$  number of cycles for one instance of K() running in software/hardware;

<sup>&</sup>lt;sup>1</sup> (1) and (2) are derived from an exhaustive analysis of all possible cases with different relations between  $T_{\rm C}$ ,  $T_{\rm r}$ , and  $T_{\rm W}$ . Fig. 2 represents only one of the 8 possible cases  $(T_{\rm W} \leq T_{\rm r} < T_{\rm C} \text{ and } T_{\rm W} + T_{\rm r} > T_{\rm C})$ .

•  $T_{\text{loop(sw)}}$  /  $T_{\text{loop(hw)}}$  - number of cycles for the loop nest with K() running in software/hardware (considering that the unroll factor satisfies the condition  $u < u_{\text{m}}$ ):

$$T_{\text{loop(sw)}} = (T_{\text{SW}} + T_{K(\text{SW})}) \cdot N \tag{4}$$

$$T_{\text{loop(hw)}} = (T_{\text{SW}} + \max(T_{\text{r}}, T_{\text{W}})) \cdot N + (T_{\text{c}} + \min(T_{\text{r}}, T_{\text{w}})) \cdot N(u)$$

(5)

The speedup at loop nest level is:

$$S_{\text{loop}}(u) = \frac{T_{\text{loop(sw)}}}{T_{\text{loop(hw)}}}$$

(6)

For  $u < u_m$ ,  $T_{loop(hw)}$  is a monotonic decreasing function; as  $T_{loop(sw)}$  is constant, it means that  $S_{loop}(u)$  is a monotonic increasing function for  $u < u_m$ .

When multiple kernels are mapped on the reconfigurable hardware, the goal is to determine the optimal unroll factor for each kernel, which would lead to the maximum performance improvement for the application. For this purpose, we introduce a new parameter to the model: the calibration factor F, a positive number decided by the application designer, which determines a limitation of the unroll factor according to the targeted trade-off. (For example, you would not want to increase the unrolling if the gain in speedup would be with a factor of 0.5%, but the area usage would increase with 15%.) The simplest relation to be satisfied between the speedup and necessary area is:

$$\Delta S(u+1,u) > \Delta A(u+1,u) \cdot F$$

where  $\Delta S(u+1,u)$  is the relative speedup increase between unroll factors u and u+1:

$$\Delta S(u+1,u) = \frac{S(u+1) - S(u)}{S(u)} \cdot 100 \ [\%]$$

(7)

and  $\Delta A(u+1,u)$  is the area increase. Since all kernel instances are identical, the total area grows linearly with the number of kernels and  $\Delta A(u+1,u)$  is always equal to the area utilized by one kernel instance  $(Area_{(K)})[\%]$ ).

Thus, F is a threshold value which sets the speedup bound for the unroll factor ( $u_s$ ). The speedup bound is defined as:

$$\mathbf{u}_{S} = \min(u)$$

such that  $\Delta S(u+1,u) < F \cdot Area_{(K)}$ .

Note that when the analyzed kernel is the only one running in hardware, it might make sense to unroll as much as possible, given the area and memory bounds ( $u_a$  and  $u_m$ ), as long as there is no performance degradation. In this case, we set F=0 and  $u_S=u_m$ .

Local optimal values for the unroll factor u may appear when u is not a divisor of N, but u+1 is. To avoid this situation, as S is a monotonic increasing function for  $u < u_{\rm m}$ , we add another condition for  $u_{\rm S}$ :  $\Delta S(u_{\rm S}+2,u_{\rm S}+1) < F \cdot Area_{(K)}$ .

By using (4) and (5) in (6) and the notations

$$x = \frac{T_{\mathrm{C}} + \min(T_{\mathrm{r}}, T_{\mathrm{W}})}{(\max(T_{\mathrm{r}}, T_{\mathrm{W}}) + T_{\mathrm{SW}}) \cdot N} \quad \text{and} \quad y = \frac{T_{\mathrm{SW}} + T_{K(\mathrm{SW})}}{\max(T_{\mathrm{r}}, T_{\mathrm{W}}) + T_{\mathrm{SW}}},$$

the total speedup is computed by:

$$S_{\text{loop}}(u) = \frac{y}{1 + x \cdot N(u)}$$

(8)

On the base of (8) and given the fact that the maximum unrolling factor is known – being the number of iterations N –, binary search can be used to compute in  $O(\log N)$  time the value of  $u_S$  that satisfies the conditions  $\Delta S(u_S+1,u_S) < F \cdot Area_{(K)}$  and  $\Delta S(u_S+2,u_S+1) < F \cdot Area_{(K)}$ .

Integrated constraints. In the end, speedup, area consumption and memory accesses need to be combined in order to find the feasible unroll factor, given all constraints. If  $u_S < \min(u_a, u_m)$ , then the optimal unroll factor is  $\min(u)$  such that  $u_S < u \le \min(u_a, u_m)$ ; else, we choose it as  $\max(u)$  such that  $u \le \min(u_a, u_m)$ .

#### 5 Experimental Results

The purpose of this section is to illustrate the presented method which computes automatically the unroll factor taking into account the area constraints and profiling information. The result and also the performance depend on the kernel implementation. The order of magnitude of the achieved speedup in hardware compared to software is not relevant for the algorithm, although it influences its output. Instead, we analyze the relative speedup obtained by running multiple instances of the kernel in parallel, compared to running a single one.

The loop from Fig. 3, containing the DCT kernel (2-D integer implementation), was extracted from MPEG2 encoder multimedia benchmark and executed on the VirtexII Pro board. We used the following parameters: width = 64, height = 64,  $block\_count = 6$  (the picture size is  $64 \times 64$ , leading to N = 96 iterations).

The DCT implementation operates on  $8 \times 8$  memory blocks, therefore one kernel performs 64 memory reads and 64 memory writes. The memory blocks in different iterations do not overlap, thus there are no data dependencies and the first assumption in Section 3 holds.

Fig. 3. MPEG2 loop with DCT kernel

The VHDL code was **automatically** generated with DWARV [3] tool and synthesized with Xilinx XST tool of ISE 8.1; it is not optimized, each memory access and each loop are synchronization points. One instance of the DCT kernel uses 12% of the total available area on VirtexII Pro. The execution times measured using the PowerPC timer registers presented in Table 1 are for one DCT instance (including the parameter transfer using exchange registers).

|            | Hardware  | Software   | Percent | Speedup |

|------------|-----------|------------|---------|---------|

| $T_K$      | 37 278    | 106 626    | 34.96%  | 2.86    |

| $T_{par}$  | 5 292     | 5 292      | 100%    | -       |

| $T_{loop}$ | 4 093 308 | 10 751 868 | 38.07%  | 2.63    |

**Table 1.** Initial execution time (cycles)

We used the following notations: (i)  $T_K$  - the number of cycles for one instance of the DCT kernel; (ii)  $T_{par}$  - the number of cycles for CPar(); (iii)  $T_{loop}$  - the number of cycles for the loop nest.

The experiment was performed with one instance of the kernel running on the FPGA. We extrapolated these results for all possible unroll factors, computing the number of cycles for software and hardware execution of the kernel, and also for the loop nest. We observe that the theoretical (computed) execution time (in cycles) for the loop nest  $(T_{\rm loop})$  with the kernel executed in software does not depend on the unroll factor. Comparing with the measured execution time, there is an error of approx 0.072%, due to not taking into account the loop overhead; this error is negligible. Next, we compute the unroll factor applying the method described in Section 4.

**Area.** The upper bound that satisfies the area constraints is:

$$u_{a} = \left[\frac{Area_{(total)} - Area_{(Molen)}}{Area_{(DCT)} + Area_{(interconnect)}}\right] = 8.$$

**Memory accesses.** For the considered implementation, the shared memory has an access time of 3 cycles for reading and storing the value into a register and 1 cycle for writing a value to memory; since there are 64 memory reads and 64 memory writes,  $\min(T_{\rm r}, T_{\rm w}) = 64$  cycles. The computation time is  $T_{\rm c} = T_{K({\rm hw})} - (T_{\rm r} + T_{\rm w}) = 37\,022$  cycles. Using these values in (1),  $\Rightarrow$  u<sub>m</sub> = 579.

**Speedup.** To compute the speedup limit  $u_S$ , we use the data from Table 1. Thus,  $T_{\rm par} = 5\,292$ ,  $T_{K(\rm sw)} = 106\,626$ ,  $T_{\rm c} = 37\,022$ ,  $\max(T_{\rm r}, T_{\rm w}) = 192$ , N = 96, then  $x \approx 0.07$  and  $y \approx 20.9$ . According to (6),  $S_{\rm loop}(u) \approx \frac{20.9}{1 + N(u) \cdot 0.07}$ .

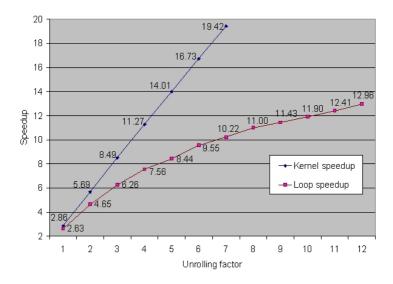

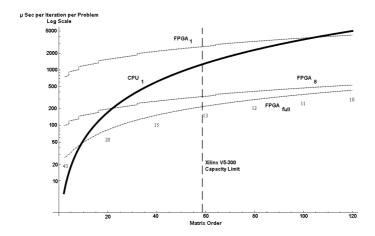

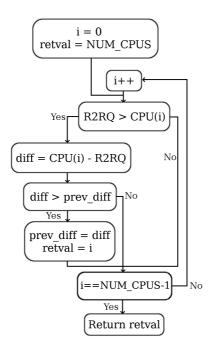

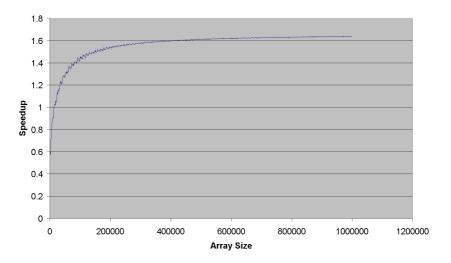

Figure 4 presents the speedup for different unroll factors. One is the speedup at kernel level, and the second at loop level.

Fig. 4. Speedup obtained with loop unrolling

Assuming that we are interested in a relative speedup increase greater than the area increase  $(\Delta S(u+1,u) > Area_{(K)})$  and  $\Delta S(u+2,u+1) > Area_{(K)})$  for two consecutive unroll factors,  $\Rightarrow u_S = 6$ .

Integrated constraints. The condition  $u_s < min(u_a, u_m)$  is satisfied, meaning that u = 6, leading to a loop speedup of 9.55 and 72% area utilization of the VirtexII Pro total area.

#### 6 Conclusion and Future Work

In this paper, we presented a method to automatically compute the optimal number of instances of a kernel K that will run in parallel on reconfigurable hardware by applying loop unrolling. The algorithm uses only the profiling information about memory transfers, execution times in software and hardware, and information about area usage for one kernel instance and area availability. Its implementation in the compiler decreases the time for design-space exploration and makes efficiently use of the hardware resources.

One of the main benefits of this algorithm is that it can be used to improve performance even when given an already optimized VHDL implementation of the kernel, if there are enough resources available (for instance, when moved to a different platform). Different results will be obtained for different kernel implementations, depending on how much optimized they are.

The presented method takes into account the area constraints when running multiple applications on the reconfigurable hardware, but not the memory constraints for this case. This will be addressed in future work. However, as our approach demonstrates the potential for significant performance improvement (experimental results for DCT show a speedup with a factor of 9.55, for an automatically generated VHDL implementation of the kernel), we plan to extend it by combining loop unrolling with pipelining and considering also transfers from a slow memory (DRAM).

#### References

- Vassiliadis, S., Wong, S., Gaydadjiev, G.N., Bertels, K., Kuzmanov, G., Panainte, E.M.: The MOLEN Polymorphic Processor. IEEE Transactions on Computers, 1363–1375, (October 2004)

- 2. Panainte, E.M., Bertels, K., Vassiliadis, S.: The PowerPC Backend Molen Compiler. In: Becker, J., Platzner, M., Vernalde, S. (eds.) FPL 2004. LNCS, vol. 3203, pp. 434–443. Springer, Heidelberg (2004)

- Yankova, Y.D., Kuzmanov, G., Bertels, K., Gaydadjiev, G., Lu, J., Vassiliadis, S.: DWARV: DelftWorkbench Automated Reconfigurable VHDL Generator. In: The 17th International Conference on Field Programmable Logic and Applications (FPL 2007) (August 2007), pp. 697–701 (2007)

- Guo, Z., Buyukkurt, B., Najjar, W., Vissers, K.: Optimized Generation of datapath from C codes for FPGAs. In: DATE 2005: Proceedings of the conference on Design, Automation and Test in Europe (March 2005), pp. 112–117 (2005)

- Gupta, S., Dutt, N., Gupta, R., Nicolau, A.: Loop shifting and compaction for the high-level synthesis of designs with complex control flow. In: DATE 2004: Proceedings of the conference on Design, Automation and Test in Europe (February 2004), pp. 114–119 (2004)

- Mei, B., Vernalde, S., Verkest, D., Man, H.D., Lauwereins, R.: Exploiting Loop-Level Parallelism on Coarse-Grained Reconfigurable Architectures Using Modulo Scheduling. In: DATE 2003: Proceedings of the conference on Design, Automation and Test in Europe (March 2003), pp. 296–301 (2003)

- Cardoso, J.M.P., Diniz, P.C.: Modeling loop unrolling: approaches and open issues.

In: Pimentel, A.D., Vassiliadis, S. (eds.) SAMOS 2004. LNCS, vol. 3133, pp. 224–233. Springer, Heidelberg (2004)

- 8. Weinhardt, M., Luk, W.: Pipeline vectorization. IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems, 234–248 (February 2001)

- Liao, J., Wong, W.F., Mitra, T.: A model for hardware realization of kernel loops. In: Y. K. Cheung, P., Constantinides, G.A. (eds.) FPL 2003. LNCS, vol. 2778, pp. 334–344. Springer, Heidelberg (2003)

- Banerjee, S., Bozorgzadeh, E., Dutt, N.: PARLGRAN: parallelism granularity selection for scheduling task chains on dynamically reconfigurable architectures. In: ASP-DAC 2006: Proceedings of the 2006 conference on Asia South Pacific design automation (January 2006), pp. 491–496 (2006)

## Programming Reconfigurable Decoupled Application Control Accelerator for Mobile Systems

Samar Yazdani<sup>1,2</sup>, Joël Cambonie<sup>1</sup>, and Bernard Pottier<sup>2</sup>

STMicroelectronics, Grenoble 38019, France samar.yazdani@univ-brest.fr

Université de Bretagne Occidentale LESTER, CNRS, Brest 29200, France

Abstract. This paper presents an innovative multimedia reconfigurable accelerator for mobile systems associated to a programming model and a compiler flow. The architecture implements a flexible memory subsystem based on software controlled scratchpad shared memory banks. The main concern of the paper is shared memory management as it is a dominant factor in current designs and influences the performance of embedded systems as well as their energy consumption. An embedded shared-memory programming model is presented that abstracts the details of the hardware architecture but yet exposing parallelism to the user. It is open and user friendly while the hardware can execute complex data feeding on heavily pipelined datapath for compute intensive kernels. The architecture has been designed, and synthesized for 65nm technology for an operating frequency of 200MHz.

**Keywords:** coarse-grain architecture, shared-memory programming model, multimedia applications, embedded systems.

#### 1 Introduction

Many application circuits available in the market today adopt a heterogeneous multiprocessor "SoC" architecture, based on a control processor (often an ARM controller), one or several DSP cores, a set of dedicated hardware IPs which perform the heavy computation burden, and an interconnect network to support the data transfers between compute blocks and memories. In addition, a low power silicon technology allows a low clock speed operation, in the order of a few hundreds of MHz, to meet the stringent power requirements of the mobile terminal.

The use of reconfigurable accelerators is attractive to avoid the presence of several processing IPs, and to keep high flexibility. This paper will present such an accelerator with aspects of its software support. The hardware implements

<sup>&</sup>lt;sup>1</sup> System on Chip.

R. Woods et al. (Eds.): ARC 2008, LNCS 4943, pp. 15-26, 2008.

<sup>©</sup> Springer-Verlag Berlin Heidelberg 2008

an array of compute resources and reconfigurable routing network, providing high acceleration ratio for iterative kernels execution as found in multimedia applications.

A very powerful addressing mechanism allows synchronized concurrent accesses on a multibanked memory thus sustaining high data throughput for the compute nodes. This level of performance is mandatory to support the needs of portable multimedia applications of the incoming years. The proposed architecture shows good adaptability and scalability characteristics, preserving the possibility to implement complex algorithms due to its shared memory orientation.

We know that it is not enough to offer hardware support for the evolution of the integrated portable platforms toward more applications and denser technologies. It is also mandatory to provide an easy access to the huge computing power of this platform to the programmer through an adequate programming model, and proper tools. To meet this strong requirement, the details of the hardware architecture are abstracted, but yet exposing parallelism to the user. The programming model based on shared memory is open and user friendly while the hardware can execute complex data feeding on heavily pipelined datapath for compute intensive kernels.

The paper outline is as follows. Section 2 describes the target architecture model implemented in 65nm technology. Section 3 describes the programming concepts, with a discussion on dynamic aspects of the execution model. Section 4 gives a brief account of compiler flow. Related work is presented in section 5 and application results are presented in section 6.

#### 2 Architecture

#### 2.1 Reconfigurable Decoupled Application Control Architecture

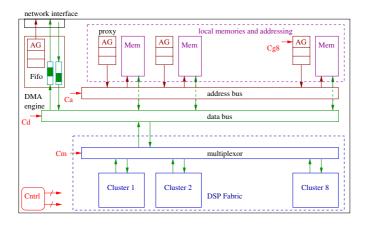

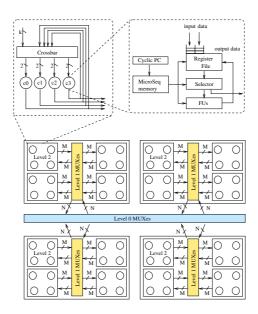

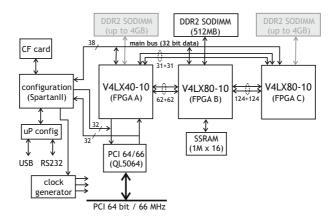

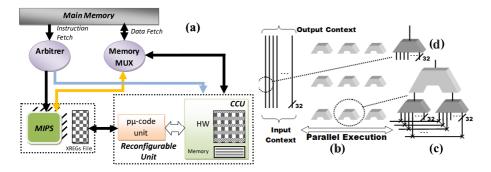

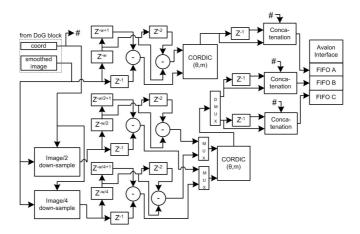

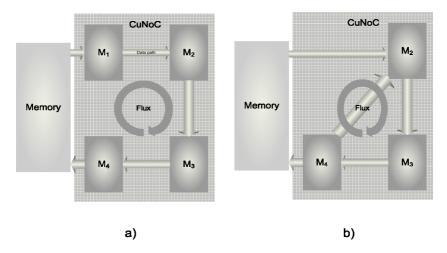

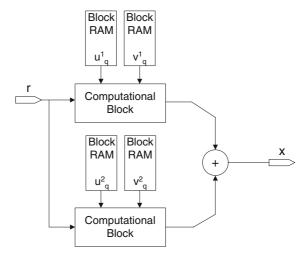

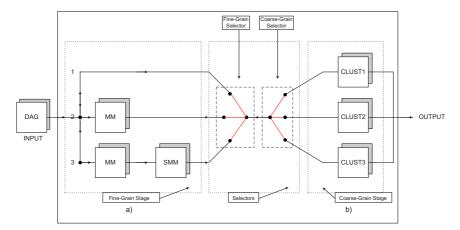

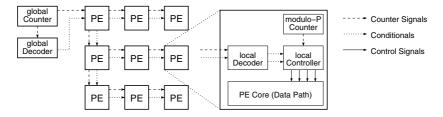

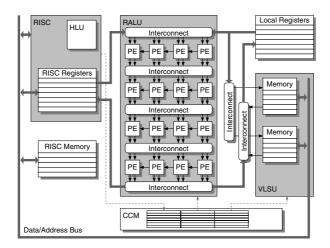

The target Reconfigurable Multimedia Accelerator (RMA) is in the category of access/execute decoupled architecture. We refer this architecture as an  $\rm RMA^2$  accelerator. Figure 1 shows the internal organization of our current target.

In an RMA architecture, an external control processor (CP) is in charge of setting up and monitoring the components for a given application execution. This CP is not shown here since it relies on specific reconfiguration and control support.

The blocks appearing in the RMA architecture are as follow:

Address Generators (AG): 3 of thems are displayed on the right part. Another one appears in the main memory DMA engine.

**DMA engine:** Connected to a network on chip (NoC) interface, in relation with 2 FIFOs for decoupling local execution from NoC and main memory availability.

Clusters: Grouped around a multiplexor allowing exchange between them and local memories or DMA engine. Clusters are data path enabling to set-up computation graphs. The DSP Fabric holds the clusters and their multiplexor.

$<sup>^{2}</sup>$  Reconfigurable Decoupled Application Control.

Fig. 1. Reconfigurable Multimedia Accelerator (RMA) block diagram

Address bus: Shared by all the local addressing mechanisms.

**Data bus:** Allows exchanges between the local memories, the FIFO internal to the DMA engine, and the DSP fabric.

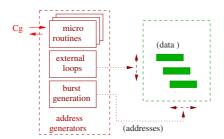

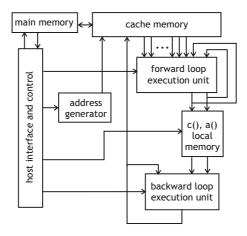

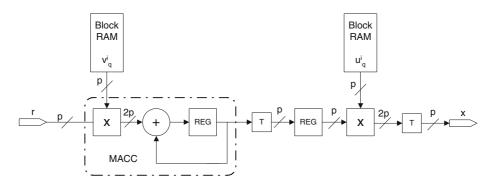

The control of the RMA comes partly from the configuration and AG microprograms participating in the configuration. A Control Unit (CU) also receives its program from the configuration, this program being the dynamic part of the control. The CU is connected to all the control points shown on figure 2.

Fig. 2. Addressing mechanism block diagram producing data structure accesses

Address generators (AG) are an assembly of three components hierarchically connected by control lines:

Burst Generators (BGen): That produces a serie of addresses based on a count and a starting point,

Address Generators (AGen): That produces the external loop over a linear data structure set-up in memory,

**Micro-control sequencement:** Defining possible repetition for address pattern generation in terms of micro-routines.

All the memory accesses are thus to be defined as AG microprogram configuration, including for main memory accesses. The CU program is critic since it must bind the feeding of the compute part to the address generation part. As there is a lot of potential concurrency in data use and communication, there is also a serious problem in coordinating the data transfers and conflicts.

The architecture can also be seen as a tighly coupled shared memory machine with conflicts resolved with a hardware support.

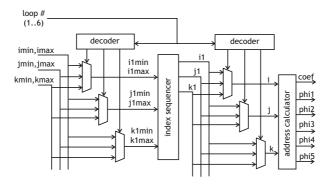

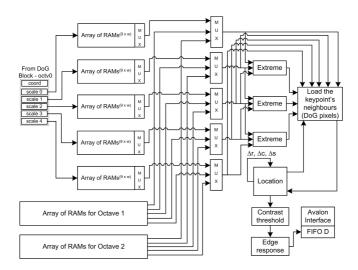

**DSPFabric description.** Figure 3 gives an overall picture of a 64 nodes/16 clusters DSPFabric co-processor. At level 0, it can be seen as an array of four 16-issues PEs, communicating through a collection of multiplexers, which realize a multi input/output switch.

Fig. 3. Hierarchical clustered DSPFabric

Each cluster set has N input wires and N output wires, output wires being possibly broadcasted to all the others. At the contrary, input wires can be connected to only one source. Figure 3 shows a feasible data path at level 0, assuming N equal to 4. At level 1, the spatial structure replicates itself inside each set of clusters, presenting again an array of 4-issue processors, connected together by multiplexers with capacity M. The last level is composed of computation node (CNs) connected through a reconfigurable crossbar, which takes as input the internal connection and K of the wire incoming from level 1. Each

computation node has two incoming wires and one outgoing wire. The computation nodes are single issue pipelined machines, accessing their own register file and functional units. Since DSPFabric has been specifically designed as loop accelerator coprocessor, each cluster is equipped with hardware features for better executing modulo scheduled code[1] like support for instruction predication and rotating registers. Precisely, the application is scheduled using the Kernel-only modulo Scheduling technique [1], which fully predicates loop prologue and epilogue. Thus, no branches are allowed and the execution is controlled by a cyclic counter. The inter-cluster copies are controlled by receive primitives executed by the destination cluster. Two regions of its register file are organized as input buffers, which push the incoming values on top, but can be read randomly by the receiver. To keep it as basic as possible, the compute node has no data memory and all temporary results and constants must be stored in the local register file, or in the memory banks of the RMA.

DSPFabric tools. Two different methods are used to map code on the DSP-Fabric. Kernel only modulo scheduling and code cloning. Kernel only modulo scheduling technique fully predicates prologue and epilogue of the loop, systematically speculates all branches of the if/then else expressions, and flattens all the internal loops in the procedure, so that a pure data flow graph expression of the algorithm is used as input to the schedule/place and route tool [2]. An other technique uses a code cloning technique, where group of nodes execute the same code shifted in time so that interconnect resources are time multiplexed between the nodes. This last method allows preservation of the control structure of the algorithm (loops are kept rolled and 'if' statement are mapped to jump instructions). In some cases, this last method can give better results that the former in terms of throughput, because inactive 'if/then/else' branches don't need to be speculatively executed.

This last method allows preservation of the control structure of the algorithm, and can give good code compaction caracteristics compared to the former.

Flexible streaming engine. The DSPFabric cyclically executes a sequence of instructions that consume and produce data through its I/Os primary ports. Those streams of data are produced by a DMA attached to that port, which reads and writes from a local buffer memory. In a steady state, a new data can be accessed on each primary port by the DSPFabric at each clock cycle, and so the maximum throughput can be sustained to feed the DSPFabric. The streaming engine has been designed to meet this high throughput requirements. It is composed of a local memory and a set of address generation units to drive the DMAs attached to the DSPFabric ports. A multibanked multiported memory block is used to store data prefetched from system memory, and to store temporary results of computation from the DSPFabric. This local buffer is useful to minimize traffic on the system interconnect, to mask bus latencies and keep a high compute efficiency for the RMA.

The DMAs of the DSPFabric ports are under control of the address generation units (AGU). This is their task to update the DMA burst descriptors. Burst

Descriptor is a structure that contains the start address, increment and last address of the memory bank under access according to the application requirements. These processors are single issue machines with an instruction memory and a data memory, and they communicate with each other through a set of shared registers that are read/write accessed by all the AGU, for instance to implement sync protocols.

### 3 Embedded Shared Memory Programming Model -Dynamic Aspects

An important aspect in streaming applications is the dataflow management between off-chip and on-chip memory hierarchies. Our data-memory architecture consists of a main memory and a scratch-pad memory. A scratch-pad memory is a fast software-managed SRAM as compared to cache-memory which is hardware-managed.

Smalltalk runtime environment (VM³) is used for the co-execution of different functional units of the heterogeneous reconfigurable accelerator (cf. section 2). The goal is to separate application from its resource management logic and to make resource management invisible from application's point of view. This abstract approach allows application validation and rapid prototyping in a unified framework. Application processes are defined as proxies. We define proxies as objects that implement a list of tasks (interfaces) specified at runtime on an instance. These tasks contribute to:

- load: pre-fetch data from virtual memory to SPM banks.

- **transmit**: feed data to the execution unit(s).

- retrieve: write back filtered data from execution unit(s) back to SPM banks.

- store: write data from SPM banks back to the virtual memory

The behavior of tasks is specified at method-level as:

- the natural encapsulation provided by methods can be used to drive hardware-software partitioning

- it facilitates capturing the method invocation by injecting specialized objects (discussed later)

- process and context management can be handled efficiently and dynamically

#### 3.1 Method Wrappers

A transition of the execution state of a program module occurs when a designated program module is called or returns from another program module, and when the other program is called or returns from the designated program module. The first step is to detect method invocation calls. In the second step, using detection of calls

<sup>&</sup>lt;sup>3</sup> Virtual Machine.

and returns among program modules as triggers, transitions in execution state are recorded, and the execution state of the designated program module is managed.

The transition between the objects is managed by injecting specialized objects *method wrappers* [3], referred MW hereafter. It allows to determine dynamically who calls a method, and which methods are called. In this manner, the communication between objects can be tracked and traced.

MW is a technique by virtue of which it replaces the method calling selector or symbol with a new one which in turn invokes the old method. Thus, changing the compiled method associated with a symbol or selector handles message-passing control. It also specializes the controlling method which is called each time the encapsulated method is invoked. For example, pseudocode below illustrates the encapsulation of a method by beforeMethod and afterMethod.

```

controlMethod(argument)

//beforeMethod

[//original method source]

//afterMethod

```

At each invocation of the original method, the *controlMethod* is called. As a natural consequence, we can:

- track the method invocations of all the methods that have been installed with MW

- change at runtime what executes before and after the original method

The latter point is the key to handle proxies (described earlier) dynamically.

#### 3.2 Dynamic Execution

At runtime, beforeMethod is efficiently used for context analysis. The decisions or conditions that require context switch could be determined before the execution of the method itself. The object which calls current active method is called sender while the object being is called receiver. Analyzing this sequence during execution helps in the application analysis. Encapsulation interfaces cause the control method to be called at each invocation and hence allows to deduce the active objects in the input application. We rely on this runtime analysis to schedule memory accesses and allocate optimally the data from virtual memory to scratch-pad memory banks.

#### 3.3 Memory Access Scheduling

In a multi-threaded environment, synchronization between concurrent threads is a critical aspect. Our solution is based on lock-free synchronization of shared data structures. A shared object is lock-free (nonblocking) if it guarantees that whenever a thread executes some finite number of steps, at least one operation on the object by some thread must have made progress during the execution of these steps. We rely on runtime scheduling which guarantees the atomicity of operations dynamically. At each macro-pipeline step all the active tasks are

analyzed. Clock step and memory access projection of each thread's memory access is determined by native code analysis. Bounding rectangles by loop indices analysis are determined for each thread's access. The overlap between bounding rectangles representing memory access durations helps in the conflict inference between concurrent threads. Runtime analysis also allows to record execution steps of each concurrent thread. Complete control of local states of active objects as stated earlier allows to record the active or inactive phases of parallel application execution.

The algorithms 1 and 2 illustrate the steps of the methodology described above.

## **Algorithm 1.** Algorithm for lock-free dynamic memory allocation management in the shared SPM banks

```

Require: A linked list of processes: P_{List}

Require: Sorting Queue: S_{queue}

Ensure: initialize method wrappers

while time_{observed} < time_{simulation} do

select process P_i from P_{List}

evaluate beforeMethod

if P_i != P_{root} then

memory access analysis (cf. Algorithm 2)

schedule memory accesses

sort the tasks in list, S_{queue}

(by giving priority to write access over read)

P_i suspend

set context to the process P_j of S_{queue}

evaluate executeMethod

end if

end while

```

#### Algorithm 2. Runtime memory access analysis

```

Require: Processes sampled for a macro-pipeline step: P_{sampled} num \Leftarrow size of P_{sampled} while num!= 0 do calculate memory access projection (bounding rectangles) determine access duration (native code analysis, start clock step, stop clock step) num \Leftarrow num - 1 end while

```

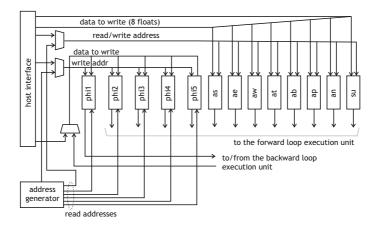

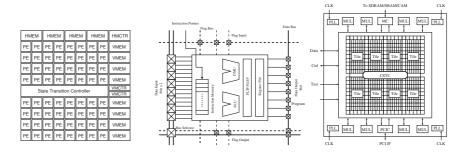

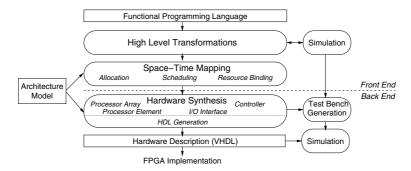

### 4 Synthesis for Architecture

A comprehensive high-level synthesis system requires step-by-step transformations of system specification or description with an objective of overlapping

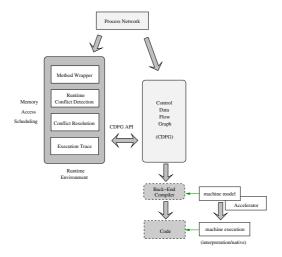

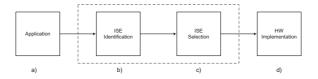

Fig. 4. Compiler Flow

computation and communication optimally. In addition to this, it requires an adequation of such transformations into a set of available system components which could be synthesized and validated. A complete flow of our framework is shown in figure 4.

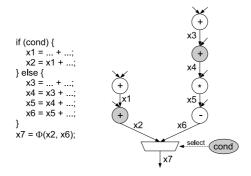

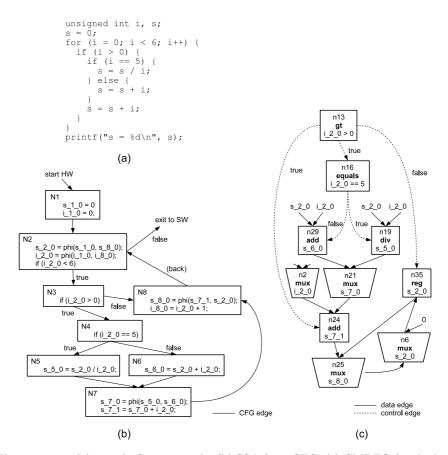

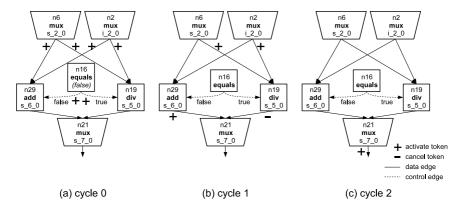

Design of an appropriate intermediate representation (IR) is of crucial importance to the effectiveness of an HLS environment. Our intermediate representation, CDFG, captures simple operators, hierarchical constructs and control structures. Hierarchical constructs are used both for readability and to force parallel/sequential execution of branches/processes of the CDFG. The control structure of the algorithm is reflected from conditional statements, loops, function call, etc. Concurrency appears at two levels: application process nodes and a control structure inside the CDFG (parallel nodes). In addition to these elements, synchronization is achieved through send/receive operations over channels.

The representation, IR, is then scheduled vis-à-vis the architectural constraints to generate code for the target architecture. This code which represents the data and program memory mappings specific to an application execution drives the structural model of the architecture. This execution is traced/visualized with a discrete-event simulator which represents the gantt-diagram of the overall execution. The framework is expected to integrate synthesis, co-simulation, performance estimation and design space exploration and graphic visualization tools.

#### 5 Related Work

Bringing flexibility to the SoC has been a research challenge for years and has lead to many proposals. Among them, the coarse grained approach has received much attention with the concept of compute intensive kernel mapped on a cluster

of very simple processing unit executing iteratively the same sequence of instructions. CoMAP[4] is an academic project proposing a weakly programmable array of processors. The cell processor [5] from IBM/Sony/Toshiba consortium proposes a cluster of processing elements with SIMD extension providing big MIPS, with a ring interconnect for nearest neighbors connections, and a centralized high throughput memory. It uses a streaming like programming model, with task level granularity. ADRES[6] is a research program from IMEC, proposing a coarse grained fabric of processing elements with a small register file and a mesh interconnect. It supports compute kernels of a few tens of operations. It is tightly coupled to a VLIW<sup>4</sup> processor for data transfers. Except some very particular cases, heavy control structures are embedded in the application code, and many are even data dependent (like in adaptive filters) and those control structures somehow decreases the benefit of using coarse grained fabric, and restrain their deployment in a low cost product. The smart memory project [7] from Stanford is an array of microcontrollers with reconfigurable distributed memory banks. It supports either a streaming like or a shared memory with cache coherence programming model. UCDavis reports an other array of processing elements with fine granularity [8], and with a streaming programming model. The fact is that all solutions showing fine granularity report high MIPS/ $mm^2$ , but are difficult to program by non architecture savvy developers. They all use a rigid memory hierarchy based on data streaming transfers that also restrict their use by a wider community.

This paper presents an innovative architecture with a flexible sub-memory system based on software controlled scratch-pad memories. The programming model is then responsible to manage data-transfers from main memory to the local memory banks. Cited methodologies related to memory allocation under the control of software can be categorized as *static* [9,10] and *dynamic* [11,12] methods.

To the best of our knowledge, none of the cited methods considers the dynamic allocation of heap data to scratchpad memory banks in a multi-threaded runtime environment which favors communication and computation overlap. In addition to the conventional memory allocation steps, the runtime environment also has to schedule explicit data transfers between the offchip memory and the SPM so as to maximize the communication and computation overlap or hide processormemory latency gap. To accomplish this, the runtime environment needs to take into account the data layout in the off-chip memory, the application access pattern, and the available memory space in the SPM.

## 6 Results - Mapping of the Deblocking Kernel on the DSPFabric

The DFG of the kernel has 376 basic nodes once loop unrolling and if/then/else to multiplexer transformation has been done. The graph is mapped on DSPFabric

<sup>&</sup>lt;sup>4</sup> Very Large Instruction Word.

| Kernel  | Number of ops | Number of     | Data rate        | Cycle budget | Schedule density |

|---------|---------------|---------------|------------------|--------------|------------------|

|         |               | compute nodes | (pix/sec)        |              |                  |

|         | 376           | 32            | 2  XVGA  30  fps | 14           | 84%              |

| MPEG-4  |               |               | (luma+chroma)    |              |                  |

| deblock |               | 16            | VGA~30~fps       | 29           | 81%              |

|         |               |               | (luma+chroma)    |              |                  |

Table 1. Mapping of the deblocking kernel on DSPFabric

using the joint scheduling/place and route method described in [2]. The mapping routine tries to make the best use of the available resources to reach a specified initiation interval for the input kernel.

Several trials have been performed targeting different initiation interval constraints, and the results are given in the table 1.

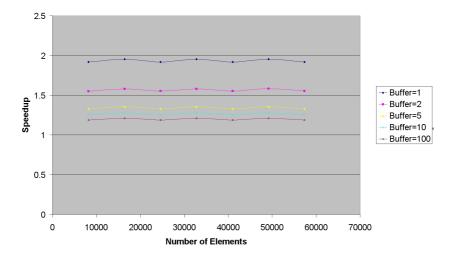

A solution with 16 nodes gives a pixel rate good enough for a VGA stream format (640×480 pixels), while with 32 nodes we sustain 2 VGA streams. This shows that performance grows linearly with the number of resources available, and this comes with a good schedule density (ration of useful operations performed during iteration execution).

#### 7 Conclusion

The results shown in this paper are still of a preliminary development , but appear very promising and worth deeper exploration of this methodology. This research is paving the way for programming toolsets and methods for massively parallel architectures with distributed memory, as envisioned in future compute platforms for portable applications.

#### Acknowledgements

This work has been achieved partly at the University of Bretagne Occidentale, LESTER, FRE CNRS, France and at STMicroelectronics, Grenoble, France. It has been funded by STMicroelectronics and ANRT CIFRE grant.

#### References

- Rau, B.R.: Iterative modulo scheduling: An algorithm for software pipelining loops. In: MICRO 27: Proceedings of the 27th annual international symposium on Microarchitecture, pp. 63–74. ACM, New York (1994)

- Sykora, M., Pavoni, D., Cambonie, J., Costa, R., Reghizzi, S.C.: Hierarchical cluster assignment for coarse grained reconfigurable coprocessor. In: Proceedings of RAW 2007, (August (2007)

- 3. Johnson, R.E., Brant, J., Foote, B., Roberts, D.: Wrappers to the rescue. In: Jul, E. (ed.) ECOOP 1998. LNCS, vol. 1445, Springer, Heidelberg (1998)

- Dutta, H., Hannig, F., Kupriyanov, A., Kissler, D., Teich, J., Schaffer, R., Siegel, S., Merker, R., Pottier, B.: Massively Parallel Processor Architectures: A Co-design Approach. In: Proceedings of the 3rd International Workshop on Reconfigurable Communication Centric System-on-Chips (ReCoSoC), Montpellier, France (June 2007)

- J.K., et al.: Introduction to the cell multiprocessor. IBM J. Research and Development, 589–604 (September 2005)

- Mei, B., Vernalde, S., Verkest, D., Lauwereins, R.: Design methodology for a tightly coupled vliw/reconfigurable matrix architecture: A case study. In: Proceedings of the Conference on Design, Automation and Test in Europe, February 16 - 20, 2004, vol. 2, p. 21224. IEEE Computer Society, Washington (2004)

- 7. Labonte, F., Mattson, P., Buck, I., Kozyrakis, C., Horowitz, M.: The stream virtual machine. In: PACT (September 2004)

- 8. Meeuwsen, M., Yu, Z., Baas, B.: A shared memory module for asynchronous arrays of processors. EURASIP Journal on Embedded Systems, 2007, Article ID 86273, 13 pages (2007)

- Avissar, O., Barua, R., Stewart, D.: Heterogeneous memory management for embedded systems. In: Proceedings of the ACM 2nd International Conference on Compilers, Architectures, and Synthesis for Embedded Systems (CASES) (November 2001)

- Banakar, R., Steinke, S., Lee, B.S., Balakrishnan, M., Marwedel, P.: Scratchpad memory: A design alternative for cache on-chip memory in embedded systems. In: Tenth International Symposium on Hardware/Software Codesign (CODES), Estes Park, May 6-8, 2002, ACM Press, New York (2002)

- Udayakumaran, S., Dominguez, A., Barua, R.: Dynamic allocation for scratchpad memory using compile-time decisions. The ACM Transactions on Embedded Computing Systems (TECS) 5(2) (to appear, 2006)

- 12. Kandemir, M., Ramanujam, J., Irwin, M.J., Vijaykrishnan, N.I., Parikh, A.: Dynamic management of scratch-pad memory space. In: Design Automation Conference, pp. 690–695 (2001)

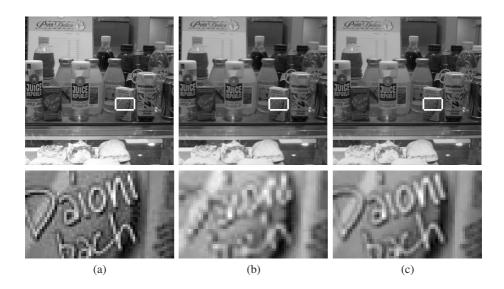

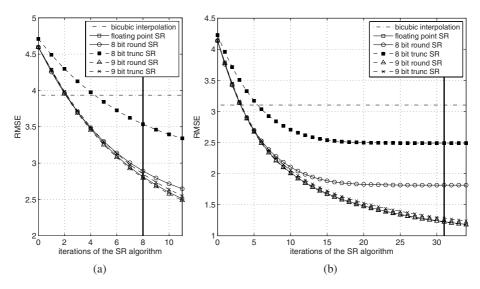

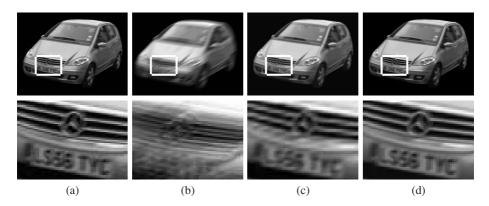

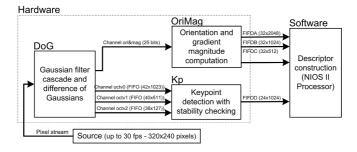

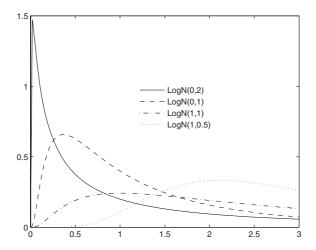

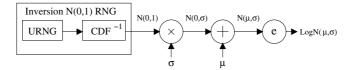

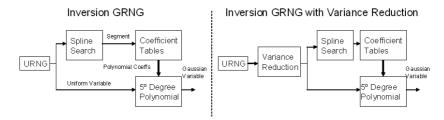

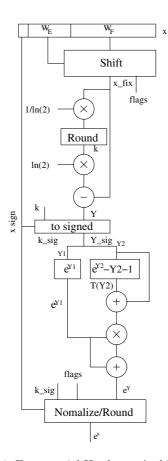

# DNA Physical Mapping on a Reconfigurable Platform